pc是什么寄存器

PC(程序计数器)寄存器是计算机体系结构中的核心组件。它不属于特殊功能寄存器,因此程序员无法直接访问它。

PC寄存器的主要责任是存储要执行的指令的地址。

在执行指令期间,PC寄存器始终指向要执行的下一个指令,以确保程序可以根据已建立的过程运行。

PC寄存器的工作机制与CPU的指令执行周期密切相关。

每次CPU执行指令时,它将从PC寄存器中读取下一个指令的地址,然后转到内存中的相应地址以获取指令并执行。

执行指令后,PC寄存器将自动更新为下一个指令的地址。

这通常是通过将1 添加到当前地址(对于固定长度指令集)或基于指令的指令跳转目标地址(对于跳跃或分支指令)来实现这一点。

此过程确保了程序和过程控制的连续执行。

PC寄存器的特性和功能可能在不同的计算环境中有所不同。

例如,在Java虚拟机(JVM)中,每个线程都有其自己的PC寄存器,该寄存器跟踪当前线程执行的Java方法的指令地址。

该设计允许多个线程同时执行,每个线程可以独立维护自己的执行状态。

当线程执行本机方法时,PC寄存器的值可能不确定,因为本地方法的执行未直接由JVM控制。

总而言之,PC寄存器是计算机体系结构不可或缺的一部分,并负责指导CPU以正确的顺序在程序中执行指令。

通过自动更新存储下一个指令的地址,PC寄存器可确保程序的连续性和正确性。

在不同的环境中,PC寄存器可能具有不同的实现方法和特征,以适应不同的需求和方案。

汇编程序中,程序员可以访问的寄存器? A程序计数器(PC) B指令寄存器(IR) C存储器数据寄存器(MDR)

A.选择。程序计数器(也称为IP)(EIP)用于存储以下命令的地址。

您可以通过呼叫,JMP和其他跳跃指南间接更改。

您可以使用移动,推动等读取值,但是您无法记录。

命令电阻器(IR)用于保存当前运行的命令。

执行命令后,将其导入内存到内存数据寄存器(MDR),然后发送到IR。

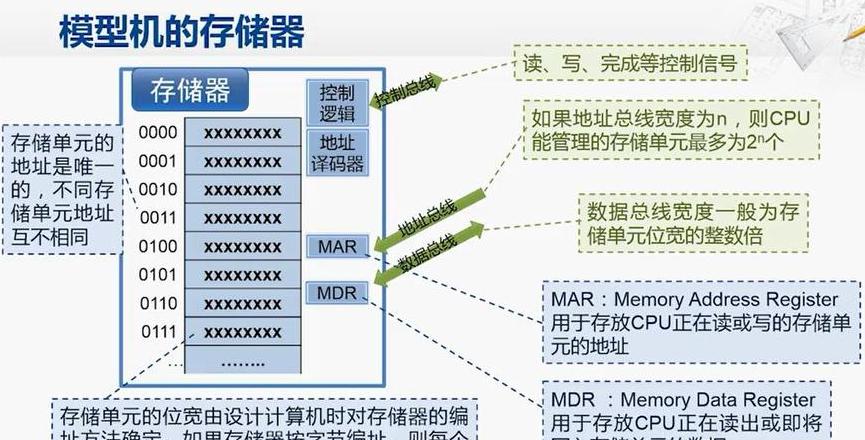

主内存与CPU之间有三个连接:主内存与CPU之间,地址总线(AB),数据总线(DB)和控制总线(CB)之间有三个连接。

将基本记忆视为黑匣子。

内存地址电阻(MAR)和内存数据电阻(MDR)是基本内存和CPU之间的接口。

3 月,您可以从程序计数器(PC)或操作数地址提交指南地址,以确定可访问的设备。

MDR是一种缓冲区组件,可在主内存中创建或读取数据。

MAR和MDR在功能上是主要内存,但通常放置在CPU上。

通用寄存器有哪些?

1 数据寄存器数据寄存器主要用于存储信息,例如操作数和计算结果,这节省了读取操作数以占用总线并访问内存所需的时间。2 索引寄存器的3 2 位处理器有两个寄存器供常规使用3 2 位ESI和EDI。

它的1 6 个较低位对应于先前CPU中的Si和DI,并且访问1 6 位较低的数据并不影响较高的1 6 位数据。

3 指针寄存器的3 2 位CPU有两个寄存器供常规使用3 2 位EBP和ESP。

它的1 6 个较低位对应于上一个CPU中的SBP和SP,并且访问1 6 个较低数据的数据不会影响较高的1 6 位数据。

4 .段的寄存器根据内存分割的管理方式定义了段的寄存器。

内存单元的物理地址由段寄存器的值和一个差异组成,因此可以在可以访问较大物理空间的内存地址中组合两个具有较少位的值。

5 指令中的指针注册3 2 位处理器将指令指示器扩展到3 2 位,并将其记录为EIP。

EIP的下部1 6 位与上一个CPU中的IP相同。

EIP和IP指令指针(DendertionPointer)是下次在代码段中执行的说明的补偿。

扩展数据寄存器是CPU内的重要数据存储资源,用于临时存储数据和地址,并且是组装程序员可以直接使用的硬件资源之一。

由于访问录制的速度比内存更快,因此在用汇编语言编写程序时,您必须尽可能多地使用注册表存储功能。

寄存器通常用于存储程序的中间结果,并迅速提供操作数以进行后续说明,从而避免在内存中存储中间结果的存储操作,然后读取内存。

在高级别的语言(例如C / C ++)中,也有一些变量定义为寄存器类型,这是改善寄存器使用的可能方法。

此外,由于寄存器的数量和能力受到限制,因此无法将所有中间结果存储在寄存器中,因此必须正确计划寄存器。

根据说明的要求,如何组织适当的寄存器并避免过度运转Opelander是一项细致而细致的任务。

参考来源:百度百科全书 - 通用登记册

通用寄存器的分类

数据寄存器主要用于存储诸如操作数和计算结果之类的信息,从而节省了使用总线和访问存储器来读取操作员所需的时间。3 2 位CPU具有4 个3 2 位通用寄存器EAX,EBX,ECX和EDX。

访问较低的1 6 位数据不会影响更高的1 6 位数据。

这些低1 6 位寄存器的命名分别为:AX,BX,CX和DX,它们与上一个CPU中的寄存器一致。

4 个1 6 位寄存器可以分为8 个独立的8 位寄存器(AX:AH-AL,BX:BH-BL,CX:CH-CL,DX:DH-DL)。

每个寄存器都有自己的名称,可以独立达到。

程序员可以通过利用数据寄存器中的“可分割和连贯”功能来灵活地对待单词/城市形成。

寄存器AX和AL通常被称为累加器,与累加器的操作可能需要更少的时间。

累加器可用于乘法,除法,输入/输出操作,并且经常使用;寄存器BX称为基础地址寄存器(基本寄存器)。

它可以用作纪念startact;注册CX称为国家议会(Countrysist)。

当您进行循环和字符串操作时,它用于控制循环数。

在位操作中,当更改多个零件时,CL被用来指示移位次数。

寄存器DX称为数据寄存器(数据寄存器)。

在执行乘法和除法操作时,可以用作标准操作数来参与操作,也可以用于保存I/O的端口地址。

在1 6 位CPU中,AX,BX,CX和DX不能用作基础地址和索引寄存器来保存存储设备的地址,但是在3 2 位CPU中,它们的3 2 位注册表可以注册EAX,EBX,ECX和EDX,而不仅仅是将数据传输数据并保存数据到存储。

因此,这3 2 位寄存器更为普遍。

有关详细信息,请参见第3 .8 节 - 有关3 2 位地址的地址方法。

3 2 位CPU有两个3 2 位的股东大会注册表ESI和EDI。

在以前的CPU中,较低的1 6 件对应于Si和Di,访问较低的1 6 个数据不会影响较高的1 6 个数据。

ESI,EDI,SI和DI寄存器称为索引寄存器(索引寄存器)。

它们主要用于存储该段中的内存单元的位移。

他们可以使用它们来实现多个纪念操作的地址方法(第3 章中详细介绍),并为不同地址表格的访问存储单元提供便利。

索引寄存器在8 位记录中是不可分割的。

作为一般寄存器,也可以存储算术逻辑操作的操作数和操作结果。

它们可以用作一般记忆指针。

在绳子手术的表现过程中,它们具有特定的要求和特殊功能。

3 2 位CPU扩展了3 2 位指令,并被指定为EIP。

较低的1 6 位EIP与上一个CPU中的IP相同。

EIP和IP(指令)指令是下次在代码段中执行的说明的偏移。

在具有前收集指令功能的系统中,除非发生转移,否则下次要进行的指令通常会推进说明队列。

因此,当您了解其功能时,不考虑说明队列的存在。

在实际模式下,由于每个段的最大范围为6 4 K,因此EIP的上部1 6 位肯定是0。

目前,使用下部1 6 件IP来反映程序中指令的执行顺序仅等效。