封装SIP和SOIC有什么区别?

经过处理的(SmallOutline集成电路包装)是一种以小格式的集成电路包装,其特征是不超过2 8 的销钉数量,它具有两种形式的包装:宽体和狭窄的身体。其中,带有短翼形电线的土壤装置称为SOJ设备,短式J型电线称为SOJ设备。

与同一浸入式包装相比,TIIC套件可节省约3 0至5 0%的空间,厚度约为7 0%。

该软件包的面额协议包括在储罐后或连续添加引脚数。

SOP(Smalloutline Package)也是1 9 7 0年代后期的集成电路包装的一种常见形式。

辅助集成技术将功能模块集成到系统中的真实包装中。

更具体地说,领带和SOP包装之间的主要区别是:1 不同的定义:TIIC是指一个不超过2 8 个外部线的集成小型电路,并且包装有两种形式:大的身体和狭窄的身体; 每个功能模块都集成到系统软件包中。

2 EIAJ标准中的TIIC宽约5 .3 毫米,通常使用SOP; 用过的。

3 不同程度的集成程度:从系统集成的角度来看,口渴是最集成的系统。

但是,TEIC无法整合被动RF电路,特别是Q高电路,例如谐振器,过滤器和高功率模块。

SOP可以通过多层三维结构(例如LTCC工艺)整合这些电路。

尽管漫画和SOP包装的大小在根本上是相同的,包括长度,销钉的宽度,销钉的间距,等等。

从芯片中,在实际应用中,它们的引脚存在一些差异。

例如,TIIC-8 缓冲垫的宽度为0.6 毫米,而SOP-8 垫的宽度为0.6 5 mm。

因此,尽管在某些情况下可以混合这两个软件包,但它们并不是完全普遍的。

集成电路系统级封装(SiP)技术以及应用

由于集成电路设计水平和过程技术的改进,集成电路的度量越来越大,并且整个系统可以集成在芯片上(目前,可以将1 08 个晶体管集成在芯片上)。它可以通过多个硬件和软件功能在系统(或Subcistam)中的单个芯片(或Subcistam)中集成。

在1 9 9 0年代后期,综合赛道进入了片上系统(SOC)时代。

在1 9 8 0年代,特殊的集成电路是通过将线路处理给设计师以标准逻辑门作为原始单元并缩短设计周期的:在1 9 9 0年代后期,他以系统为基础的芯片时代,在1 9 9 0年代后期,他进入。

在芯片上,它包括CPU,DSP,逻辑电路,模拟电路,射频电路,内存和其他电路模块以及嵌入式软件,并相互连接以创建一个完整的系统。

由于系统设计的复杂性越来越复杂,设计行业的工厂专门针对这些功能开发各种集成电路模块(称为知识产权核心或IP核心)。

这些模块已授权用于其他系统设计人员供支付使用。

设计师将使用IP核心作为设计的原始单元。

IP核心的重复使用不仅缩短了系统设计周期,而且还提高了系统设计的成功率。

研究表明,与IC制成的系统相比,由于SOC设计可以广泛考虑整个系统的各种情况,因此高系统指标与相同的过程可以在条件下获得。

2 1 世纪SOC技术将是一个真正快速的发展时期。

近年来,由于整个机器的便携式增长趋势和系统的缩影,有必要在芯片上整合更多不同类型的组件,例如C-C-C-Cimosic,GAAS-RFIC,各种被动组件,光学机械,光学机械设备,天线,连接。

诸如单一材料和标准过程之类的传感器的SOC受到限制。

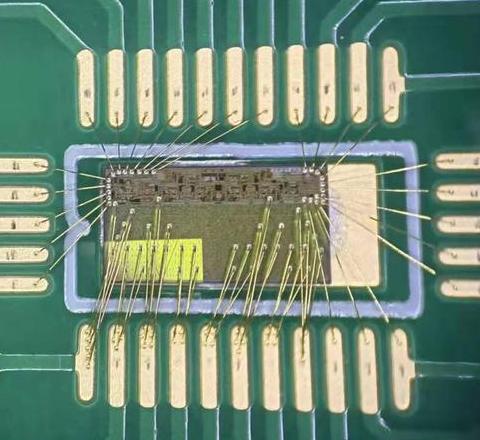

近年来,基于SOC的系统包装(SIP)不仅可以收集包装中的几个芯片,而且还可以堆叠和集成各种设备和电路芯片。

复杂,完整的系统。

与SOC相比,(1 )可以提供更多的新任务; 很容易分成碎片。

SOC和SIP相互补充。

人们普遍认为,SOC主要用于更新缓慢的产品,并针对军事设备性能的高需求。

SIP主要用于消费产品(例如手机)的低替换周期。

SIP需要进一步提高速率和计算机辅助设计。

由于下降的复杂性,因此提出了滴水的设计和过程技术的高要求。

在设计方面,包括系统工程师,电路设计,布局设计,有机硅技术设计,测试和制造的工程师团队需要共同努力,以实现最佳性能,最低尺寸和最低成本。

首先,使用计算机辅助模拟设计芯片,电源和被动组件的标准和布局是为设计而设计的。

高密度电路设计应考虑消除振荡,过冲,交叉震动和辐射。

考虑散热和可靠性; SIP采用了在过去十年中迅速发展的触发焊接互连技术。

触发焊接互连具有低直流电压,高互连密度,小寄生诱导,良好的热和电性能的优势,但成本高于焊接线。

SIP的另一个好处是能够整合各种被动组件。

集成电路迅速使用被动组件。

例如,移动电话中主动元素的被动元素的比率约为5 0:1 近年来,诸如多温度多层陶瓷(LTCC)和低温合作社的合作社(LTCF)技术,即IE,电阻器,电容器,电感器,过滤器和谐振器的无效组件。

在多层陶瓷中。

就像将活动设备集成到硅中一样。

此外,为了提高包装中芯片芯的面积比,采用了两个以上的芯片堆栈结构,并在z方向上进行了三维整合。

铜线是通过新技术开发的,例如超切片的柔性绝缘层底板,层压芯片之间,底板上的铜线,孔互连和金属化。

SIP已被广泛用于该行业的竞争,以快速进入市场,以获得小型,薄,轻巧的功能。

它是主要应用程序是RF/无线应用程序,移动通信,网络设备,计算机和外围设备,数字产品,图像,生物学和MEMS传感器。

到2 01 0年,SIP的接线密度预计为6 000 cm/cm2 ,热量密度为1 00W/cm2 ,组件密度为5 000/cm2 ,I/O密度为3 000/CM2 系统级包装设计也正在发展为计算机辅助自动化,例如自动布局和SOC的接线。

英特尔的最先进的SIP技术将五个堆叠的闪光芯片集成到1 .0毫米的超斜线套件中。

东芝的SIP目标是将手机的所有功能集成到包装中。

日本最近预测,如果LSI系统在世界上五分之一采用SIP技术,那么SIP市场将达到1 .2 万亿日元。

随着进入市场的好处,SIP将在未来几年以快速增长。

为了集中综合电路设计和芯片构建,中国应增加其在系统级包装方面的研发工作。

集成电路的封装形式有哪些

集成电路具有不同的包装表格,以满足不同的应用要求。双线包装(DIP)是最常见的形式之一,带有双行铅笔,用于简单插件和板上的连接器。

细球网格阵列(FBGA)使用球形焊接化合物,适用于高密度的连接,并且在高性能计算区域广泛。

微型四轮套件(LQFP)和塑料四合一扁包装(PQFP)是紧凑型且适用于与空间相关的电路板结构的常见形式。

双内线软件包(SDIP)和小型框架软件包(请参阅)也经常使用,该包装表格具有较小的外观,适用于便携式设备。

小型形式的晶体管(SOT2 2 0)是为晶体管设计的,并且更紧凑。

较小尺寸(TSOP)和PIN Ultraduns紧凑型包装(TSSOP或TSOPII)的薄包装进一步降低了包装尺寸并改善集成。

塑料铅芯片载体(PLCC)是带有笔的塑料包装形状,适用于各种应用方案。

这些包装形式具有自己的特性,从双线到细球网阵列,从微季度的扁平包装到塑料铅芯片载体。

为特定应用优化了每种形式的包装,以满足电子设备越来越复杂的微型化趋势。

双线包装(DIP)的特征是双线销设计,该设计有助于手动安装并在电路板上拆卸,适合各种标准开关板。

细球网眼阵列(FBGA)使用球形焊接化合物来实现高密度的连接,并且适合需要高集成和高可靠性的应用程序场景。

Micro Quad Flat套件(LQFP)和塑料Quad Flat Package(PQFP)以其小尺寸而受欢迎,适用于空间有限的电路板结构。

双线包装(SDIP)和小框架软件包(请参阅)通常也用于其紧凑的外形。

小型晶体管晶体管(SOT2 2 0)是为晶体管设计的,更紧凑,适合晶体管应用。

较小尺寸(TSOP)和PIN超薄紧凑型软件包(TSSOP或TSOPII)的薄软件包进一步降低了包装尺寸,改进集成,并且经常用于便携式设备和功能强大的计算字段。

塑料铅芯片载体(PLCC)的设计配有笔,适合各种应用程序,包括便携式设备和服务器。

集成电路封装技术的发展可分为哪几个阶段 集成电路封装技术发展趋势

1 集成电路包装技术的开发阶段是什么? 集成电路包装技术跨越四个阶段:1 适用于印刷电路。衡量芯片包装技术是否先进的重要指标是,芯片区域和包装区域之间的比率越多,该包装技术的比例就越高。

由于芯片区域和包装区域之间的关系很大,因此包装完成后的体积相对较大。

2 表面组装阶段8 0年代是表面组装的时代。

一些记忆生产者仍采用改进的TSOP技术。

3 其次,有芯片尺寸(CSP)的数据包,带有无铅(PQFN)和多芯片组件(MCM)的四面菜肴。

与芯片开发以达到芯片发展的节奏相比,BGA技术开发的成功终于允许包装。

在集成电路的包裹中。

4 从原始包装组件的概念到包装系统,他经历了革命性的变化,主要包括基于包装的芯片包装(SOC)和微观机械系统包装(MEMS)。

2 对于具有多个数字的胶片的开发,芯片可以使用芯片包装具有更多不同的功能。

2 3 高级包装技术的开发扩展并扩展了包装和集成处理过程的概念,可以通过“包装”从WAPH到系统描述。

系统级封装技术综述

摘要软件包技术摘要,Zung Xueen剪辑以及如何解决带翼包装和解决带翼问题的问题。与系统芯片插座相比,SIP专注于多芯片和低性能解决方案以及集成高性能解决方案。

传统的包装技术通过洪水的阶段,当地人的发展水平开放了杰克房间。

Smip获得高力量的权力区,等等。

与SCO相比,SIP的面积很小,价值相似和更舒适的测试过程,尤其是对于区域市场。

尽管SIIP和MM,这两种技术都被认为是随着工作和价格收益的未来而培养的。

SIP具有非常好的Chaip巴士性能,并且由良好的次要董事会媒体,低功率和广泛的设计关系完成,以提高系统性能。

SIP应用技术技术包括次要机构,3 D Myders和犯罪水平包装(WLP)。

Modccomoponsk技术减少了减少水文凭的模块的文凭,以及最高的工作包装和FC连接技术。

这些技术促进了SIP包装技术开发和广泛的应用。

简而言之,系统级包装CIP,设计师,变量,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,经济,有效,并表明了广泛的市场承诺。