ic design 芯片设计的流程是怎么样的

芯片设计的过程通常始于需求定义,包括确定功能和性能测量,电气性能,柴油,功耗和TDA(测试设计自动化)定义。此阶段对于确保后续设计满足最终产品的所有要求至关重要。

定义要求后,输入RTL(寄存器传输级别)设计阶段。

在此阶段,设计团队使用硬件说明语言来描述芯片的行为和功能。

RTL设计是整个设计过程的核心。

完成RTL设计后,立即进行仿真和验证。

通过不同的测试用例,请确保RTL设计满足性能和功能要求。

此步骤可能需要重复迭代以确保设计的正确性。

此后,执行逻辑合成以将高级RTL描述转换为端口级别的Web列表,并插入设计可测试性功能)以支持后续的测试过程。

正式验证用于验证逻辑合成的结果是否满足设计要求。

在物理综合中,为特定的设备块绘制了逻辑Web列表,并生成了最终的在线列表。

此过程决定了芯片的物理设计,包括哪些单位块位于哪个位置。

在设计和接线阶段,根据物理合成的结果执行特定的布局和电线。

此步骤需要评估信号完整性和功率完整性等因素,以确保设计的物理实施符合期望。

设置验证确保设计和路由的结果符合设计规则和规格。

寄生参数提取用于在电路中提取寄生虫参数,例如对手,电容器等,以提供准确的数据以进行后续模拟。

仿真后是为了验证物理设计,以确保在实际生产条件下仍可以满足设计要求。

在淘汰阶段,最终设计将对作品本身进行。

芯片后的转向水平和功能确认的验证确保芯片的最终性能和功能。

51单片机 汇编语言 常用数据处理程序设计 查表送寄存器

LI MicroController会议语言编程,常用信息处理程序设计包括一个注重的表查找。该程序从特定的存储位置和过程中读取数据。

DPR(信息规则)上的第一个点为存储表的地址。

表以特定顺序排列的表上的数据从查看表中获取所需的信息值。

例如,org000000h标记程序的启动地址和movdptr,#table表示DPR必须指向名为表的存储区域。

接下来,在r2 中的寄存器中的信息商店中的一个时间存储中的movr2 和指令以随后使用。

Movca, @ a + DPR培训检索值以抵消寄存器上的信息,即从表上的特定位置读取数据。

然后,它建立在R0寄存器中,并使用XCHA和R2 指令将临时值与新值定律交换为R0当前计算所需的数据。

该程序准备通过增加寄存器中的值来读取下一个数据字节。

再次使用MOVCA, @ + DPR指令,以读取R1 寄存器中下一个商店的其他信息字节。

最后,使用SJMP $ $跳到当前电子邮件中,只是在循环中执行。

具体而言,org2 000H定义了表格,表,dw0、1 、1 、1 6 、2 5 、3 6 、4 9 、6 4 、8 1 、1 00、1 2 1 、1 4 4 、1 4 4 、1 6 9 、1 9 9 、2 6 9 、2 2 5 、2 2 5 、2 5 6 、2 8 9 、3 2 4 ,3 2 4 、3 6 1 、4 00、4 4 1 、4 8 4 、5 2 9 、5 7 6 、6 7 6 、6 7 6 、7 2 9 、7 8 4 、8 4 1 该表提供了该程序的数据源,允许该程序从查看表中获取信息。

可以连续处理由手柄(例如信息上的信息)实施的整个过程。

这意味着,数据可以是较软的处理和使用,而无需直线编码。

寻找发件人表的模式是通过处理指定信息集的有效处理,最合适的预定义信息需要频繁访问和处理。

这种方法仅简化了编程,但也可以提高代码的可读性和可维护性。

在实际应用中,可以将各种函数值,控制参数或预定义的数值表存储在表中,并且可以通过查找表来快速获得所需的数据,从而优化程序的执行效率。

mux寄存器作用

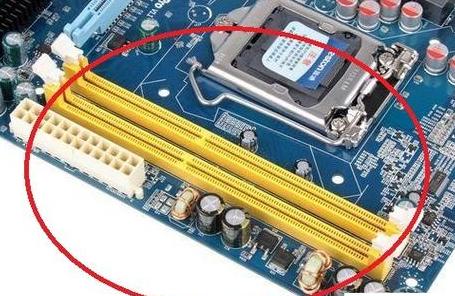

MUX寄存器功能:用于临时存储数据和计算结果,并具有接收数据,存储数据并发送数据的功能。寄存器的阅读速度和写作速度很高,并且寄存器之间的数据传输非常快。

寄存器的主要功能是临时存储参与操作的数据和计算结果,并具有接收数据,存储数据和发送数据的功能。

寄存器具有很高的读写和编写速度复制,并且寄存器之间的数据传输非常快。

触发器用于保存二进制代码。

MUX寄存器设计:描述复杂的硬件电路,设计人员始终将复杂的功能共享成简单的功能,模块是提供每个功能的基本结构。

设计人员可以使用“自上而下”的想法在低级模块中共享复杂的功能模块。

此步骤通常是由系统级负责人设计的,而较低的模块是由设计师在下一级别完成的。

使用Verilog描述硬件的基本设计单元是一个模块。

复杂电子周期的构建主要是通过模块的其他交通电话实现的。

该模块包含在关键字模块和结束模块中。

实际电路组件。

Verilog模块类似于C-语言功能。